# HETEROGENEOUS SYSTEM AND APPLICATION COMMUNICATION MODELING

#### BY

#### CARL PEARSON

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2018

Urbana, Illinois

Adviser:

Professor Wen-Mei Hwu

## ABSTRACT

With the end of Dennard scaling, high-performance computing increasingly relies on heterogeneous systems with specialized hardware to improve application performance. This trend has driven up the complexity of high-performance software development, as developers must manage multiple programming systems and develop system-tuned code to utilize specialized hardware. In addition, it has exacerbated existing challenges of data placement as the specialized hardware often has local memories to fuel its computational demands. In addition to using appropriate software resources to target application computation at the best hardware for the job, application developers now must manage data movement and placement within their application, which also must be specifically tuned to the target system. Instead of relying on the application developer to have specialized knowledge of system characteristics and specialized expertise in multiple programming systems, this work proposes a heterogeneous system communication library that automatically chooses data location and data movement for high-performance application development and execution on heterogeneous systems. This work presents the foundational components of that library: a systematic approach for characterization of system communication links and application communication demands.

$To\ my\ family,\ for\ their\ love\ and\ support.$

## ACKNOWLEDGMENTS

I would like to thank my thesis advisor, Professor Wen-Mei Hwu. He allowed me to make this my own work, but his door was always open when I needed guidance.

I would also like to thank the members of the IMPACT research group for their insight and assistance, and for creating such a fruitful research environment.

I would also like to thank Isaac Gelado of Nvidia for his technical insights that contributed to the results described in this thesis.

I would also like to acknowledge Dominic Grande who collaborated extensively in the development of the software tools described in this thesis.

Finally, this work is supported by the following two entities:

- The IBM-Illinois Center for Cognitive Computing Systems Research (C<sup>3</sup>SR) a research collaboration as part of the IBM Cognitive Horizon Network.

- The Blue Waters sustained-petascale computing project, which is supported by the National Science Foundation award OCI-0725070 and the state of Illinois. Blue Waters is a joint effort of the University of Illinois at Urbana-Champaign and its National Center for Supercomputing Applications.

# TABLE OF CONTENTS

| LIST OF TABLES                           | /ii                  |

|------------------------------------------|----------------------|

| LIST OF FIGURES                          | iii                  |

| LIST OF CODE LISTINGS                    | ix                   |

| LIST OF ALGORITHMS                       | Х                    |

| LIST OF ABBREVIATIONS                    | xi                   |

| CHAPTER 1 INTRODUCTION                   | 1                    |

| CHAPTER 2 BACKGROUND                     | 4<br>4<br>5          |

| 2.3 PCIe and NVLink Interconnects        | 6<br>9<br>16         |

| 2.6 OpenMP                               | 18<br>19             |

| v                                        | 20<br>22             |

| 3.1 Joint Abstraction and Hardware Model | 27<br>27<br>28       |

| 4.1       CPU / CPU Transfers            | 32<br>32<br>35<br>43 |

|                                          | 48<br>49             |

| 5.1 Coherence vs. Prefetch Bandwidth     | 55<br>60             |

| 5.3 Summary                              | 64                   |

|            | TER 6 FUTURE WORK: APPLICATION CHARACTER-                             |

|------------|-----------------------------------------------------------------------|

| IZA        | FION AND COMBINED MODELING                                            |

| 6.1        | Measuring Additional Communication Capabilities                       |

| 6.2        | Mapping Logical Communication to Underlying Links                     |

| 6.3        | Application Model                                                     |

| 6.4        | Constructing the Dynamic Value Dependence Graph for                   |

|            | Unmodified Applications                                               |

| 6.5        | Combined Modeling                                                     |

| 7.1<br>7.2 | System Topology Enumeration / Hardware Models System Characterization |

|            | NUMA / Multi-GPU APIs                                                 |

|            | TER 8 CONCLUSION                                                      |

| REFER      | ENCES                                                                 |

| APPEN      | IDIX A: FULL TOPOLOGIES                                               |

# LIST OF TABLES

| 2.1 | Interconnect performance summary               | 7 |

|-----|------------------------------------------------|---|

| 2.2 | PCIe lane transfer rates                       | 8 |

| 2.3 | Basic memory-management APIs                   |   |

| 2.4 | CUDA pinned memory-management APIs             | 2 |

| 2.5 | System support for GPU-GPU peer access         | 3 |

| 2.6 | CUDA unified memory-management APIs            | 4 |

| 2.7 | Nvidia DGX-1 architecture summary              | 3 |

| 2.8 | IBM S822LC architecture summary                | 4 |

| 2.9 | IBM AC922 architecture summary 20              | 6 |

| 3.1 | Discoverable vertex types                      | 0 |

| 3.2 | Discoverable edge types                        |   |

| 4.1 | Affinity and logical communication bandwidth 4 | 1 |

| 4.2 | Host-device transfer anisotropy                |   |

| 4.3 | Transfer rate on identical CPU-GPU links       | 3 |

| 4.4 | Transfer rate on identical GPU-GPU links 4     | 7 |

| 5.1 | Device affinity and coherence bandwidth        | 8 |

| 5.2 | Device affinity and prefetch bandwidth         | 9 |

| 5.3 | Anisotropy in coherence bandwidth              | 9 |

| 5.4 | Anisotropy in prefetch bandwidth 60            | 0 |

| 5.5 | Page fault latencies                           | 3 |

# LIST OF FIGURES

| 2.1 | System abstraction                                | 5  |

|-----|---------------------------------------------------|----|

| 2.2 | Example system interconnect bandwidths            | 6  |

| 2.3 | Example PCIe and NVLink interconnect topologies   | 7  |

| 2.4 | Example of NUMA bandwidth effects on AC922        | 17 |

| 2.5 | Nvidia DGX-1 architecture schematic               | 23 |

| 2.6 | IBM S822LC architecture schematic                 | 25 |

| 2.7 | IBM AC922 architecture schematic                  | 26 |

| 3.1 | Communication topologies exposed to application   | 28 |

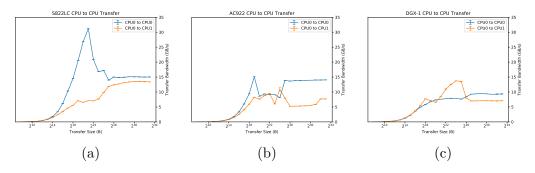

| 4.1 | CPU-CPU transfer bandwidth                        | 35 |

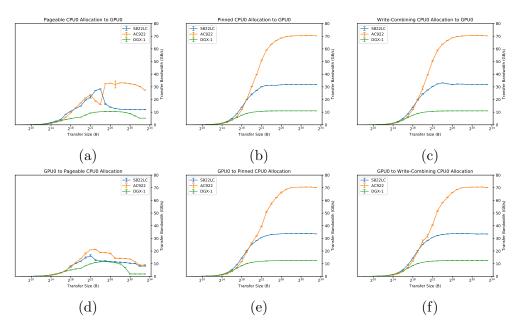

| 4.2 | CudaMemcpy bandwidth for CPU0-GPU0 transfers      | 37 |

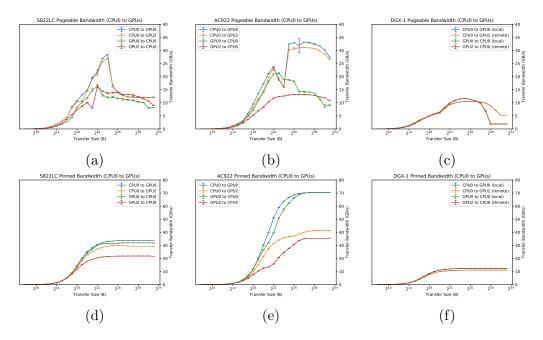

| 4.3 | CPU-GPU affinity and cudaMemcpy bandwidth         | 39 |

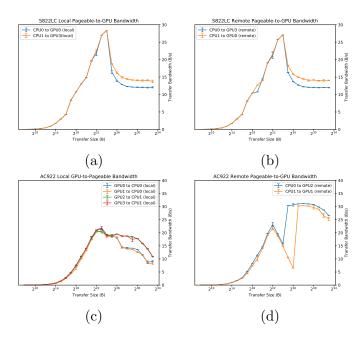

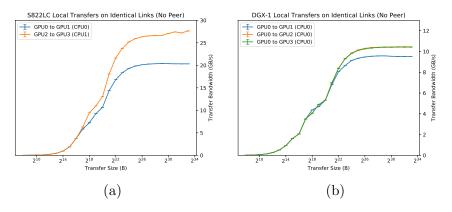

| 4.4 | CPU/GPU cudaMemcpy bandwidth on identical links   | 43 |

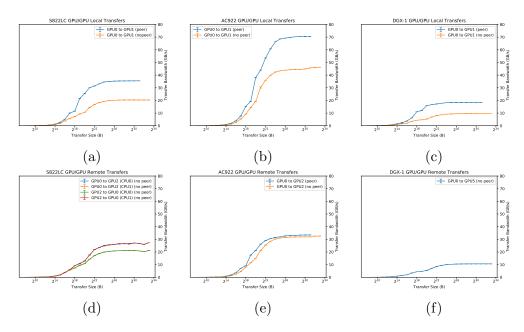

| 4.5 | GPU-GPU cudaMemcpy bandwidth and peer access      | 46 |

| 4.6 | GPU-GPU cudaMemcpy Bandwidth on Identical Links   | 48 |

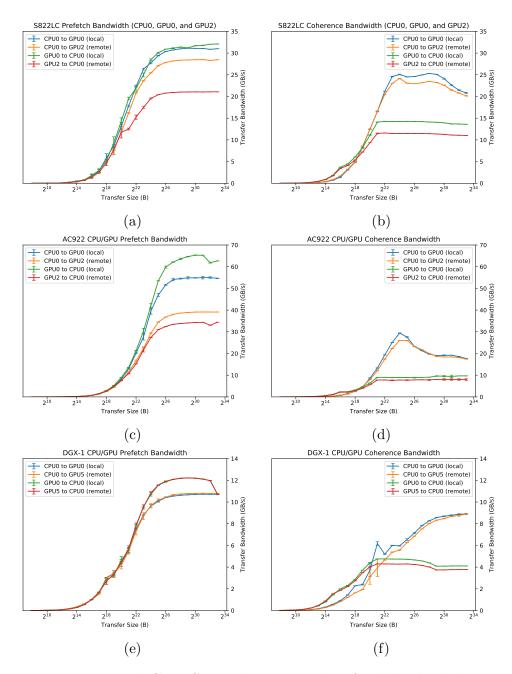

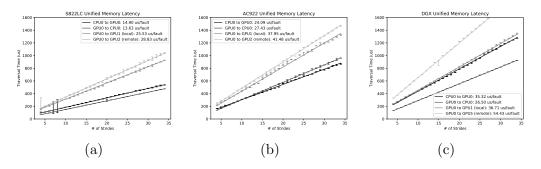

| 5.1 | CPU/GPU coherence and prefetch bandwidth          | 55 |

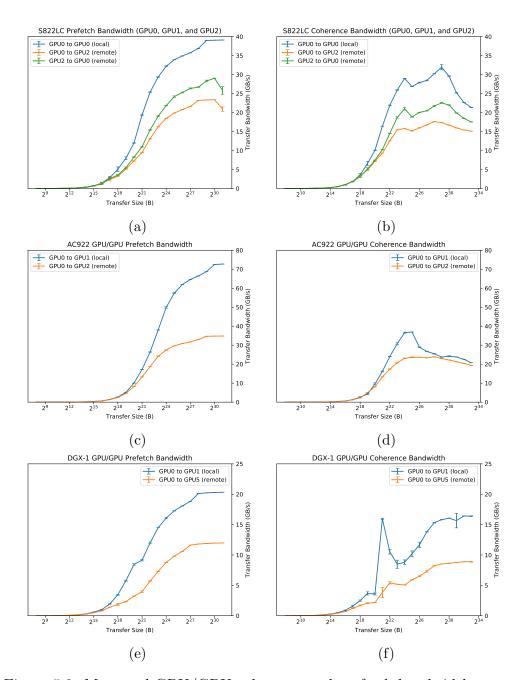

| 5.2 | GPU/GPU coherence and prefetch bandwidth          | 57 |

| 5.3 | Page fault latencies for S822LC, AC922, and DGX-1 | 64 |

| 6.1 | Dynamic value dependence graph                    | 68 |

| A.1 | S822LC discovered topology                        | 83 |

| A.2 | AC922 discovered topology                         | 83 |

| A.3 | DGX-1 discovered topology                         | 84 |

# LIST OF CODE LISTINGS

| 2.1 | Binding to NUMA nodes                                | 17 |

|-----|------------------------------------------------------|----|

| 2.2 | Measuring time with CUDA events                      | 19 |

| 2.3 | Benchmark with automatic timing                      | 21 |

| 2.4 | Benchmark with manual timing                         | 22 |

| 5.1 | cpu_write function                                   | 53 |

| 5.2 | gpu_write function                                   | 54 |

| 5.3 | GPU linked list traversal kernel for Algorithm 5.6   | 61 |

| 5.4 | CPU linked list traversal function for Algorithm 5.5 | 63 |

# LIST OF ALGORITHMS

| 2.1 | Bind OpenMP threads to a NUMA node                               | 18 |

|-----|------------------------------------------------------------------|----|

| 4.1 | Measure cudaMemcpy CPU-CPU bandwidth                             | 33 |

| 4.2 | Pageable, pinned, and write-combining host allocators            | 34 |

| 4.3 | Measuring CPU/GPU bandwidth with ${\tt cudaMemcpy}$              | 36 |

| 4.4 | Measuring GPU-GPU cudaMemcpy peer bandwidth                      | 44 |

| 4.5 | Measuring GPU-GPU $\operatorname{cudaMemcpy}$ non-peer bandwidth | 45 |

| 5.1 | Measuring GPU-GPU unified memory coherence or prefetch           |    |

|     | bandwidth                                                        | 50 |

| 5.2 | Measuring CPU-GPU unified memory coherence or prefetch           |    |

|     | bandwidth                                                        | 51 |

| 5.3 | Measuring GPU-to-CPU unified memory coherence bandwidth.         | 52 |

| 5.4 | Measuring GPU-to-CPU unified memory prefetch bandwidth.          | 53 |

| 5.5 | Unified memory page fault latency: CPU destination               | 61 |

| 5.6 | Unified memory page fault latency: GPU destination               | 62 |

## LIST OF ABBREVIATIONS

CUDA Compute Unified Device Architecture

FPGA field-programmable gate array

GPU graphics processing unit

NUMA non-uniform memory access

RAM random-access memory

SIMD single-instruction multiple-data

SMP symmetric multi-processing

## CHAPTER 1

## INTRODUCTION

With the end of Dennard scaling, computer architects have sought to satisfy demand for increasing performance by providing specialized hardware accelerators tuned to computation with particular characteristics. Perhaps the most successful example of this trend is the widespread adoption of graphics processing units (GPUs) for more general data-parallel compute tasks. With the success of GPUs as a template, architects are moving forward with a wide variety of accelerators, such as SIMD extensions [1, 2, 3], AI accelerators (Google tensor processing unit [4], Huawei Neural Processing Unit [5], IBM neuromorphic chips [6], Intel Nervana [7]), motion coprocessors (Apple M-series [8]), field-programmable gate arrays (Xilinx Virtex [9], Intel Stratix [10]), network processors (Netronome Agilio [11]), digital signal processors (Qualcomm Hexagon [12], NXP DSP56xx Family [13]), vision processing units (Eyeriss [14], Movidius VPU [15], Mobileye EyeQ [16], Microsoft Holographic Processing Unit [17]) and many others.

The enormous compute capability of accelerators demands high-bandwidth access to data to "feed the beast." Without this access, the performance potential of the accelerator is largely wasted waiting for data. The trend of *integration* (also motivated by reduction of total system cost) where semiconductor die-size or power limits allow, has provided one approach to solving this problem. By integrating an accelerator onto the same die as the CPU, the accelerator more easily gets high-bandwidth low-power access to data shared with the CPU. For accelerators with high memory demands, however, the system memory DRAM bandwidth may ultimately limit performance.

The second approach is to provide accelerators with their own highperformance memory. Unfortunately, managing this memory then falls upon runtime systems or the application developer, and moving data into accelerator memory to support high-performance execution is a first-order design consideration for any accelerated application. The data-placement and data-movement challenge is exacerbated by the growing demand for data-driven applications. Analytics and neural-network applications ingest huge amounts of data, and even if the amount of compute per data element is small, the aggregate required computation can be commensurately large. That motivates developers to use accelerators for these applications. To achieve high performance on accelerators, developers must marshal and coordinate their data movement and computation.

This work describes an automated approach to analyzing the performance of data movement in systems that use discrete accelerators with local memories. Broadly, the approach consists of two components: a system characterization tool, which enumerates and characterizes the performance of logical communication paths, and an application characterization tool, which profiles unmodified applications to record how they interact with the system. These tools are examined in the context of heterogeneous systems made of CPUs and Nvidia GPUs and machine-learning workloads due to the maturity of that hardware/software ecosystem. Together, these tools provide a foundation for automating analysis of the relationship between system design and application performance.

In pursuit of that vision, this work makes the following contributions:

- a detailed communication performance characterization of three multi-CPU/multi-GPU systems designed for data-driven applications (Chapters 4 and 5)

- a novel hardware enumeration tool for enumerating undirected graph hardware topologies in multi-CPU/multi-GPU systems (Chapter 3)

- an approach for combining this characterization with an application characterization to understand application performance on modern accelerator-heavy systems (Chapter 6)

The rest of this document is organized as follows: Chapter 2 describes background information on the studied computers, the CUDA programming system, Linux NUMA system, OpenMP, and profiling tools proposed for the application characterization; Chapter 3 describes the hardware system characterization approach; Chapter 4 describes performance characterization of explicit CUDA memory management. Chapter 5 describes performance

characterization of unified memory in CUDA systems. Chapter 6 describes future work of application characterization and combined modeling. Chapter 7 discusses related work; and finally, Chapter 8 concludes.

## CHAPTER 2

## BACKGROUND

This work examines the relationship between system and application performance in the context of systems comprised of CPUs and Nvidia GPUs. To that end, Section 2.1 describes the relationship between software abstractions and the underlying system hardware, Section 2.2 discusses how Nvidia graphics processing units (GPUs) fit into the computing system architecture, Section 2.3 describes the PCIe and NVLink interconnect systems used to couple GPUs to each other and the rest of the system, Section 2.4 details communication-related components and APIs of CUDA, the Nvidia GPU programming system, Sections 2.5 and 2.6 describe the Linux non-uniform memory access (NUMA) and OpenMP multiprocessing systems, Section 2.7 describes the Linux and CUDA components used in the proposed application profiler, and Section 2.9 documents the heterogeneous systems used as case studies in this work.

## 2.1 System Communication Abstraction

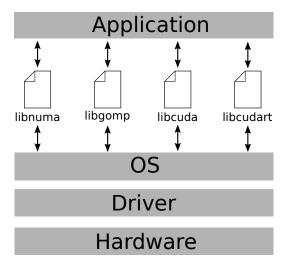

Application access to computing systems is made through a stack of abstractions. This work considers applications that interface with the system through CUDA, the Linux NUMA abstraction, and OpenMP. Those API calls are implemented in various libraries, such as libcudart.so on Linux systems. In turn, those libraries make use of system calls provided by the operating system. The operating system interfaces with various drivers, including the Nvidia GPU drivers and the interconnect drivers, to make use of the underlying hardware. Figure 2.1 shows a schematic of this stack.

Through these layers of abstraction, the underlying communication capabilities are modified. For example, PCIe interconnects transfer data with packets, but the CUDA API does not expose the ability to create custom

Figure 2.1: The application interacts with the underlying hardware through libraries, the operating system, and drivers.

packets to send to the GPU. Furthermore, the performance of the hardware is modified. For example, when CUDA unified memory is used, some of the link bandwidth may be consumed by control signals that help ensure data coherence. Chapters 4 and 5 show how different uses of the CUDA API can achieve different performance on the same physical hardware.

## 2.2 GPUs and System Architecture

Nvidia GPUs used in high-performance computing are fully-discrete accelerators. From the software side, they demand explicit management through the Nvidia Compute Unified Device Architecture (CUDA) programming system: a set of C++ language extensions and libraries. In a GPU-accelerated application, the CPU typically acts as a manager and "offloads" specialized compute tasks to the GPU. From the hardware perspective, GPUs are separated from the CPU and memory by an interconnect link. The GPU has its own local memory, which must be populated with data for the GPU to operate on. For the rest of this thesis, we will refer to the system memory associated with that CPU as the "CPU memory" or "system memory", and the GPU's local memory as "GPU memory". Finally, though not covered in this work, the GPU compute cores have dramatically different performance characteristics than CPU cores, and require specialized programming styles.

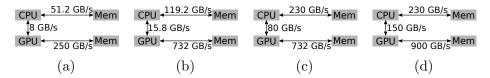

Figure 2.2 shows some example interconnect bandwidth numbers for some

Figure 2.2: Representative interconnect bandwidths between CPU and system memory, GPU and GPU memory, and CPU to GPU. (a) shows a c.2011 x86 system with an AMD Operton 6200 CPU [18] system, PCIe 2.0 x16, and Nvidia K20 GPU. (b) shows a c.2017 x86 system with an Intel Xeon Platinum 8180M [19] CPU, PCIe 3.0 x16, and an Nvidia P100 GPU. (c) shows a c.2013 PowerPC system with an IBM Power8 [20] CPU, two-lane NVLink 1.0, and an Nvidia P100 GPU. (d) shows a c.2017 PowerPC system with an IBM Power9 [21] CPU, three-lane NVLink 2.0, and an Nvidia V100 GPU.

hypothetical systems. In all cases, the bandwidth between the CPU or GPU and their respective memories is much higher than the bandwidth between the CPU and GPU. In older systems and current x86 systems, that link may be an order of magnitude slower than the other interconnects. The vastly different link performance makes data placement extremely important for application performance.

Figure 2.2a is representative of a node of a supercomputer designed in 2012 [22]. Figure 2.2b represents a similar system, with components updated to 2017. Figure 2.2c is a c.2013 system with an IBM Power8 CPU and NVLink 1.0. Figure 2.2d represents next-generation interconnect bandwidths present in the Summit [23] and Sierra [24] supercomputers delivered in 2018.

### 2.3 PCIe and NVLink Interconnects

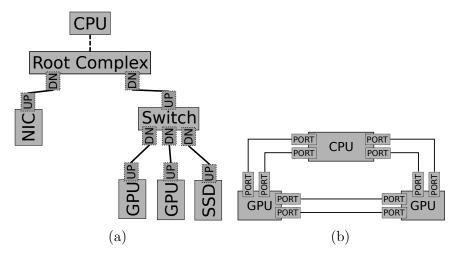

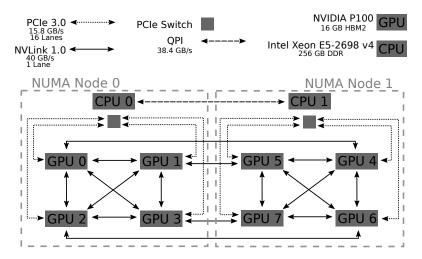

Modern systems with discrete GPUs feature either NVLink or PCIe accelerator interconnects. These interconnects couple the GPUs to the CPUs and/or other GPUs. Table 2.1 summarizes the theoretical bandwidth of common interconnect configurations. Figure 2.3 shows example PCIe and NVLink topologies. Section 2.4.4 describes how these topologies affect parts of the CUDA peer-communication API.

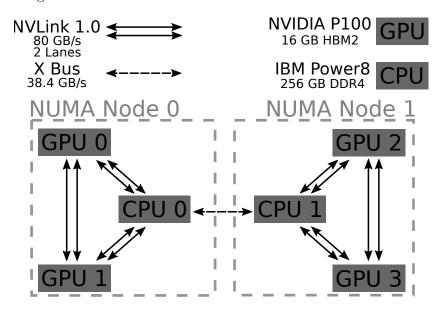

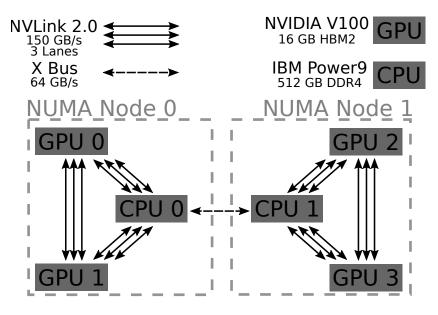

The Nvidia DGX-1 system (Section 2.9.1) uses PCIe to connect CPUs to GPUs, and single-lane NVLink 1.0 to connect amongst GPUs. The IBM S822LC system (Section 2.9.2) uses two NVLink 1.0 lanes to connect pairs

Table 2.1: Theoretical performance for common interconnect configurations. Only NVLink configurations used in the case studies are shown below. PCIe 3.0 x16 is included for reference, as most PCIe 3.0-attached GPUs use 16 lanes.

| Interconnect      | Bandwidth            | Year | Architecture   |

|-------------------|----------------------|------|----------------|

| PCIe 3.0          | 15.8 GB/s (16 lanes) | 2012 | Tree           |

| NVLink 1.0 / NVHS | 20 GB/s (1 lanes)    | 2016 | Point-to-Point |

| NVLink 1.0 / NVHS | 40 GB/s (2 lanes)    | 2016 | Point-to-Point |

| NVLink 2.0 / NVHS | 75 GB/s (3 lanes)    | 2017 | Point-to-Point |

Figure 2.3: (a) An example PCIe topology, showing the root complex at the root of the tree, with endpoints and switches connected by links. (b) An example NVLink topology, with each device supporting four NVLinks, and using two to connect to each of its neighbor devices.

of devices, with each lane operating at 20 GB/s. The IBM AC922 system (Section 2.9.3) uses three NVLink 2.0 lanes to connect pairs of devices, with each lane operating at 25 GB/s.

#### 2.3.1 PCIe

Peripheral Component Interconnect Express (PCIe) is an expansion bus standard [25]. PCIe components form a tree, rooted at the *root complex*. PCIe devices such as GPUs or SSDs are *endpoints*, with a single upstream port and no downstream ports. Data is sent point-to-point between participating endpoints and/or the root complex via unique PCIe addresses. The topology also may include *switches*, components with a single upstream port and

multiple downstream ports. Switches do not receive data packets, and are only used to extend the topology. Components are connected by PCIe *links*, each of which consists of one to 32 lanes. The total bandwidth of the link depends on the PCIe generation and the number of lanes. Figure 2.3a shows an example topology. The PCIe 3.0 specification [26] was finalized in 2010, and the first Nvidia GPUs to support it were some Kepler-architecture products released in 2012 [27].

Table 2.2 shows single-lane PCIe bandwidths from generation 1.0 to 3.0. Physically, each PCIe lane has four wires, divided into two differential signaling pairs. A PCIe 3.0 x16 interconnect therefore has 64 wires. In PCIe 3.0, each signaling pair operates at 8 Gb/s. With a 128b/130b encoding, this gives PCIe 3.0 x16 a 15.8 GB/s unidirectional bandwidth.

**PCIe Revision** Signaling Rate **Encoding** Line Bandwidth 1.0  $2.5 \; \mathrm{GT/s}$ 8b/10b250 MB/s $\overline{5.0}$  GT/s 2.0 8b/10b500 MB/s3.0  $8.0~\mathrm{GT/s}$ 128b/130b984.6 MB/s

Table 2.2: PCIe lane transfer rates

#### 2.3.2 NVLink

NVLink is a communication protocol developed by Nvidia. Current NVLink implementations use the proprietary high-speed signaling interconnect NVHS [28]. Like PCIe, each NVLink connects two devices. Unlike PCIe, there is no concept of upstream or downstream ports, and devices may have multiple ports. Multiple links may connect devices, in which case the links are combined to contribute to the available bandwidth between devices. Figure 2.3b shows an example topology. The NVLink 1.0 systems in this work allow each device to have four NVLink lane connections, with each lane running at 20 GB/s [29], [30]. The NVLink 2.0 systems in this work allow each device to have six NVLink lanes at 25 GB/s each [31].

Physically, each bidirectional lane has 32 wires, divided evenly into two unidirectional sublinks of eight differential pairs [28]. Each pair operates at 20 Gb/s for NVLink 1.0 and 25 Gb/s for NVLink 2.0. This means a 2-lane NVLink 1.0 has 64 wires. The improved bandwidth of 2-lane NVLink 1.0 vs. PCIe 3.0 is directly attributable to the signaling rate on the wires.

### 2.4 CUDA

Nvidia's CUDA (Compute Unified Device Architecture) is a programming system for enabling general-purpose computation on Nvidia GPUs (graphics processing units). CUDA is a set of C extensions and libraries for interfacing with GPUs. Nvidia provides a compiler, nvcc, for generating CUDA-enabled binaries.

CUDA provides a set of runtime and driver APIs for the developer to manage the allocation and movement of data between the host and device memory. From its inception, CUDA provided comprehensive APIs for developers to mitigate application performance shortfalls stemming from the relatively limited performance of host-device communication links. As the capabilities of GPUs and host systems have improved, CUDA has provided simpler, higher-level APIs that require less programmer effort. This section describes CUDA memory-management capabilities and the historical context of their introduction.

The CUDA API has an associated version number that defines which CUDA actions are made available by that API. CUDA-capable hardware advertises a specific compute capability (CC) that defines what CUDA actions are supported by that GPU. Although the CUDA API may expose particular capability, the GPU may need a sufficiently high CC to take advantage of it. This section references both these version systems when discussing CUDA features.

This work focuses on the performance of explicit CUDA memory management and the CUDA unified memory system. There is a third set of transfer capabilities that fall under the umbrella of remote-mapping or "zero-copy" memory. These techniques are subsumed by unified ,emory, though making use of them typically requires hints to the CUDA system. Once the flexibility of the unified memory system improves, it will be important to revisit the performance implications of zero-copy memory.

## 2.4.1 Basic CUDA Memory and System Memory

Prior to the introduction of unified virtual addressing (see Section 2.4.3), the CUDA memory space was composed of multiple address spaces: one for the host, and one for each GPU [32]. Data was explicitly allocated

in those address spaces through cudaMalloc. Standard C/C++ memory allocation techniques (malloc/new, free/new) are used for managing memory on the host. cudaMemcpy is used to move data between address spaces, whether the host and device or between devices. Since each device has a separate address space, the programmer explicitly instructs cudaMemcpy how to move data with cudaMemcpyHostToDevice, cudaMemcpyDeviceToHost, or cudaMemcpyDeviceToDevice. Basic CUDA memory management runtime calls are described in Table 2.3.

Table 2.3: Basic CUDA and C/C++ memory-management APIs.

| CUDA API                    | Description                                   |  |

|-----------------------------|-----------------------------------------------|--|

| <pre>cudaSetDevice()</pre>  | Associate a device with the host thread.      |  |

| cudaMalloc()                | Allocate memory on the device.                |  |

| cudaFree()                  | Free memory on the device.                    |  |

| cudaMemcpy()                | Copy data between to, from, and between GPUs. |  |

| <pre>cudaMemcpyPeer()</pre> | Copy data between GPUs without CPU involved.  |  |

| C/C++ API                   | Description                                   |  |

| new / malloc()              | Allocate pageable memory on the system heap.  |  |

CudaMemcpy is only partially asynchronous with respect to the host ([33], ch. 1). It will return once the pageable source allocation is safe to modify, but possibly before the data has finished moving to the device. This impacts the design of the performance characterization routines in Chapter 4. CudaMemcpyPeer initiates a DMA copy from one GPU to another, without involving the host. This can improve the bandwidth of the transfer between supported devices. The impact of this peer access is also described in Chapters 4 and 5.

This API definition imposes the following basic structure on all CUDA programs, which remains essentially unchanged through CUDA 9.1.

- 1. Allocate memory on the host with new/malloc.

- 2. Initialize memory on the host.

- 3. Allocate memory on the device with cudaMalloc.

- 4. Copy initialized data from the host to the device with cudaMemcpy(..., cudaMemcpyHostToDevice).

- 5. Launch CUDA kernels.

- Copy results back to the host with cudaMemcpy(..., cudaMemcpyDeviceToHost).

- 7. Free CUDA allocations with cudaFree.

Unified virtual addressing (Section 2.4.3) and unified memory (Section 2.4.5) allow the data transfer steps to happen implicitly on supported systems.

### 2.4.2 Page-Locked Memory

The GPU uses direct memory access (DMA) to copy data to and from the host. When cudaMemcpy is invoked, the CPU instructs the GPU to copy a region of host memory to the device memory (or vise-versa), without the CPU being involved. The host must guarantee that the memory to be accessed by the GPU will not be paged-out during the copy. First, cudaMemcpy copies the data from the application address space to a piece of page-locked memory in the system memory managed by the CUDA driver, and then cudaMemcpy instructs the GPU to initiate the DMA from that page-locked region to the GPU memory.

The CUDA runtime functions in Table 2.4 are the core functions CUDA provides to make page-locked memory regions directly visible to the application. When the application uses these APIs, the first copy from pageable host memory to page-locked host memory can be elided. Section 4.2.1 demonstrates the performance improvement from skipping this first copy. Overuse of page-locked memory on the host will degrade overall application performance or even impact system stability if the host system is not able to page as needed.

CudaHostAlloc allows including the even more options, cudaHostAllocPortable and cudaHostAllocWriteCombined flags. CudaHostAllocWriteCombined causes a pinned allocation to be writecombined. Writes to write-combined memory may be delayed and combined in a buffer to reduce the number of memory accesses. Additionally, the host may not cache this data in L1 or L2 cache, freeing up those resources for other applications. This may prevent unnecessary cache invalidations from occurring during the DMA. Furthermore, coherency is not enforced, so data is not snooped on the PCIe bus, which can increase bandwidth by up to 40%([35], 3.2.5.2). Due to the possible lack of caching, this type of allocation

Table 2.4: CUDA pinned memory-management APIs.

| API Description    |                                    | CUDA<br>Version<br>Introduced |

|--------------------|------------------------------------|-------------------------------|

| cudaMallocHost()   | allocate page-locked memory on the | 1.0 [34]                      |

|                    | $\operatorname{host}$              |                               |

| cudaFreeHost()     | free page-locked memory on the     | 1.0 [34]                      |

|                    | host                               |                               |

| cudaHostAlloc()    | cudaMallocHost with additional     | 3.0 [35]                      |

|                    | options                            |                               |

| cudaHostRegister() | Page-lock a range of host memory   | 4.0 [36]                      |

makes sense for data that is not frequently read by the CPU, for example, data written once by the CPU before being sent to a GPU.

CudaHostAllocPortable allows all CUDA contexts to treat the memory as pinned, not just the context that performed the allocation. This became the default with the introduction of unified virtual addressing.

### 2.4.3 Unified Virtual Addressing

Unified virtual addressing was introduced with compute capability 2.0 GPUs and CUDA 4.0 on 64-bit systems. The host memory and the memory of each GPU are mapped into disjoint subsections of a single unified address space.

This enhancement simplifies several of the already-introduced CUDA memory management commands ([36], 3.2.7). The cudaMemcpyDefault flag for cudaMemcpy instructs the CUDA system to automatically determine how to move data. By examining the address of the pointers passed to cudaMemcpy, CUDA determines where which device the memory resides on and moves it accordingly. This simplifies the programmer's use of cudaMemcpy, as cudaMemcpyDefault may be used everywhere. There is also no need to call cudaHostGetDevicePointer for mapped allocations. Furthermore, all mapped allocations are automatically accessible by all GPUs in the system, not restricted to the GPU that was active at the time of the allocation. CudaMemcpyPeer is no longer needed for device-to-device memory copies; cudaMemcpy may be used instead.

#### 2.4.4 Peer Access and UVA

Peer access was introduced with CUDA 4.0. CudaDeviceEnablePeerAccess() allows CC 2.0+ devices to address memory in another device's address space ([36], 3.2.6.4). For example, if GPU1 loads through a pointer to data on GPU0, the data will be directly fetched from GPU0 memory, at the cost of one PCIe transaction and one global memory load [32], and be cached in the L2 of GPU0. Direct peer access requires compute capability 2.0, CUDA 4.0, Fermi+, and 64-bit system. The availability of peer access may rely on a combination of interconnect topology and system hardware, summarized in Table 2.5. When peer access is disabled, data transfers first pass through the host instead of allowing direct DMA between devices.

Table 2.5: GPU-to-GPU connection, and whether peer access is supported for the systems considered in this work.

| Between GPUs with           | System | Peer Access |

|-----------------------------|--------|-------------|

| a shared PCIe switch        | DGX-1  | <b>√</b>    |

| different PCIe switches     | DXG-1  | ×           |

| a direct NVLink connection  | S822LC | <b>√</b>    |

| no direct NVLink connection | S822LC | ×           |

| a direct NVLink connection  | AC922  | <b>√</b>    |

| no direct NVLink connection | AC922  | <b>√</b>    |

## 2.4.5 Unified Memory with CC 3.0+ (Kepler+)

The CUDA unified memory system was introduced with CUDA 6.0 and requires a GPU with SM architecture of 3.0 or higher [37]. CUDA unified memory [38] provides a single pool of memory that is accessible from the CPU and GPU by a single pointer. CUDA automatically migrates data between the physically distinct CPU and GPU memory as needed, allowing GPU kernels to access the memory as if it were in the global memory, and CPU functions to access the memory as if it were in the system memory. Like mapped memory, this simplifies programming by removing the need for separate host and device allocations and explicit data transfers. A summary of unified memory APIs is shown in Table 2.6.

The underlying data is only present in one location on the system, and in principle, unified memory allocations are automatically migrated towards

Table 2.6: CUDA unified memory-management APIs. Initial CUDA 6.0 APIs and additional CUDA 8.0 APIs are shown.

| CUDA 6 and CC3.0+                     | Description                          |

|---------------------------------------|--------------------------------------|

| $\_$ managed $\_$                     | Defines a global variable in managed |

|                                       | memory                               |

| <pre>cudaMallocManaged()</pre>        | allocate a unified memory region.    |

| <pre>cudaStreamAttachMemAsync()</pre> | Attach a managed allocation to a     |

|                                       | stream, instead of globally.         |

| CUDA 8 and CC6.0+                     | Description                          |

| cudaMemPrefetchAsync()                | Hint to prefetch memory to device    |

| cudaMemAdvise()                       | Hint about how memory will be used   |

their most recent use. When a kernel is launched, all pages attached to that kernel's stream are bulk migrated to the destination GPU. When the host program touches a page, that page is migrated back to the system memory. In multi-GPU systems, data does not migrate between GPUs - all other GPUs receive peer mappings to the data, which is accessed over the PCIe bus ([37], J.1.3).

Unified memory maintains coherence (i.e., all GPUs and the CPU have the same view of unified memory values) by disallowing concurrent accesses to managed data, including concurrent access to distinct managed allocations ([37], J.2.2.1). The CPU may access managed allocations after GPU execution has completed, where "GPU execution" refers to activity in a particular stream for stream-attached memory, or whole-GPU otherwise. For stream-attached memory, completion of GPU execution can be guaranteed by any stream-synchronizing call. For whole-GPU memory, completion is guaranteed by stream synchronization when only one stream is executing on the GPU, 1 or by any call that is fully synchronous with respect to the host. 2 The GPU is considered to be active even if it is not accessing managed data. Concurrent inter-GPU accesses are allowed, as are concurrently-executing kernels on a single GPU ([37], J.2.2.2).

<sup>&</sup>lt;sup>1</sup>e.g., cudaStreamSynchronize()

<sup>&</sup>lt;sup>2</sup>e.g., cudaDeviceSynchronize()

### 2.4.6 Unified Memory with CC 6.0+ (Pascal+)

With CUDA 8 and for GPUs with CC 6.0+, GPU page faulting provides a more fine-grained data transfer mechanism [39]. Instead of moving all managed allocations to the GPU prior to a kernel launch, the GPU will fault if it accesses a page that is not in its memory. The page is either migrated to the GPU to serve that access, or the page is mapped into the GPU address space to be accessed over the host-device interconnect. Unlike unified memory with CC 3.0, pages can migrate between GPUs on peer accesses ([39], J.1.4). The GPU page faulting mechanism lifts all restrictions on simultaneous access to data ([39], J.2.2.1). However, intensive interleaving of CPU and GPU accesses to a page can cause excessive migrations and result in severe performance degradation.

CC 6.0+ also brings 49-bit virtual addressing to cover the 48-bit virtual addressing of modern CPUs and the GPU memory. This allows CUDA to support managed allocations larger than the GPU memory. The total amount of managed allocations still cannot be larger than the system memory ([39], J.1.3).

CudaMemPrefetchAsync() hints to the unified memory system that a particular device will soon be accessing a unified memory allocation. This may cause the system to migrate the specific region of memory over to the referenced device. This hint is used in Chapter 4 in some of the unified memory characterizations.

CudaMemAdvise() hints to the unified memory system how a particular region of memory can be used. CudaMemAdviseSetReadMostly causes the hinted device to establish a read-only copy of a page, instead of taking complete ownership of a page on access. Any writes to that page become expensive, as all read-only copies must be invalidated. This cost is not evaluated in this work. CudaMemAdviseSetPreferredLocation hints to the driver that data migration of the page away from the device should be avoided. This may cause the system to establish a remote mapping for the data, instead of migrating the page. CudaMemAdviseSetAccessedBy hints to the driver that the device will access the memory region. It causes the page to be mapped in the device page table for as long as possible, to prevent page faults on access.

### 2.4.7 Unified Memory with CC 7.0+ (Volta+)

Though not examined in this work, Volta GPUs contain the necessary hardware for more intelligent migration of pages. When support is added in the Nvidia driver, access counters will be used to trigger page migrations of hot pages, instead of on each access. The system will also detect thrashing, and temporarily prevent page faults to allow faster progress on each device. On POWER9 systems, the CPU and GPU have access to each other's page translation hardware, allowing memory accesses on the CPU to be served from the GPU and cached on the CPU. Furthermore, the CPU can execute atomic operations on locations in GPU memory without a page migration [40].

## 2.5 Linux Non-Uniform Memory Access

Linux includes a system for exposing non-uniform memory access architectures (NUMA) to applications. In NUMA systems, memory is divided into multiple nodes [41]. Processors and devices have the same access characteristics when accessing memory in a particular node. Nodes have affinity to processors and devices, indicating the processors and devices which can access that node with the best performance.

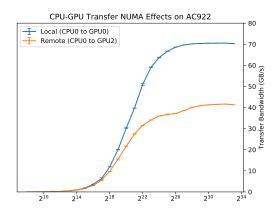

This is particularly relevant on multi-socket systems, though some single-socket systems also feature NUMA characteristics. For example, every system considered by this work and described in Section 2.9 is a NUMA system. On the AC922 (Figure 2.7), GPU0 is directly connected to CPU0 and GPU2 is directly connected to CPU1. If an allocation on CPU0 were to be copied to GPU2, the data would traverse the CPU-CPU X bus, and then the CPU-to-GPU NVLink. On the other hand, if an allocation on CPU1 were to be copied to GPU2, that data would only have to traverse the NVLink. This can have a substantial effect on available bandwidth, as shown in Figure 2.4. Chapters 4 and 5 show these effects in more detail.

Figure 2.4: Example of NUMA bandwidth effects on AC922

Applications can leverage the numactl [42] library to affect their own NUMA execution policy. This policy controls on which CPUs processes may execute, and on which NUMA nodes memory is allocated. Numactl is used in this work to ensure that data is allocated and programs execute on specific CPUs as needed to exercise different underlying hardware links. Listing 2.1 shows a C++ function that takes the operating system NUMA node ID as an integer argument and binds the executing thread and its allocations to that node. Lines 6 and 7 allocate a bitmask, and set the bit corresponding to the NUMA node. Numa\_bind() in line 8 forces execution and allocations to occur on the nodes in the nodemask.

Listing 2.1: Binding to NUMA nodes.

```

1

static inline void

numa_bind_node(const int node) {

3

if (-1 == node) {

4

numa_bind(numa_all_nodes_ptr);

5

} else if (node >= 0) {

struct bitmask *nodemask = numa_allocate_nodemask();

6

7

nodemask = numa_bitmask_setbit(nodemask, node);

8

numa_bind(nodemask);

9

numa_free_nodemask(nodemask);

10

} else {

exit(1);

11

12

}

}

13

```

The benchmarks in this paper also initialize numactl with calls to numa\_set\_strict(1) and numa\_set\_bind\_policy(1), which ensure that NUMA will cause the program to exit on an error, and that if the memory cannot be allocated on

the requested NUMA node, the allocation will fail instead of falling back to a different node.

## 2.6 OpenMP

OpenMP is a shared-memory processing system that uses compiler directives and library functions to allow applications to implement shared-memory parallel processing techniques [43]. Among other more sophisticated approaches, OpenMP allows hint-assisted parallelization of nested loops through compiler directives. This work uses OpenMP to use multiple CPU threads while transferring data between the CPU and the GPU during the unified memory characterization in Chapter 5. Multiple CPU threads are used to ensure that the CPU is generating sufficient memory traffic to saturate its memory controllers and make the maximal demands of the unified memory system. There is a runtime overhead of entering the parallelized region, which affects the design of the benchmarks.

Many microbenchmarks in this work rely on execution of threads on particular NUMA nodes. The numa\_bind(node) function binds the current process and all child processes to the provided node, but OpenMP does not necessarily implement worker threads as children of the current thread. Algorithm 2.1 is used to bind all OpenMP threads to a NUMA node. A full OpenMP thread team is created, and each of those threads individually binds itself to the provided NUMA node.

### Algorithm 2.1 Algorithm to bind all OpenMP threads to a NUMA node.

```

function OMP_NUMA_BIND_NODE(dev)

bind_cpu(dev)

for all worker threads do

bind_cpu(dev)

end for

end function

```

## 2.7 Profiling Tooling

#### 2.7.1 CUDA Events

An event is a special kind of operation that is performed in a CUDA stream. CUDA events allow the CUDA runtime to set and query noteworthy milestones in the sequence of stream operations without stalling the stream. These events may be used as a lightweight method for measuring how much time CUDA operations take without also measuring the time taken to synchronize the stream. Events are created with cudaEventCreate(), destroyed with cudaEventDestroy(), and inserted into a stream with cudaEventRecord(). CudaEventSynchronize() blocks the calling thread until a particular event has been completed in the stream. CudaEventElapsedTime() returns the number of milliseconds that have elapsed between two completed events. Listing 2.2 shows an example of measuring time of hypothetical CUDA operation cudaSomeAsyncOperation() taking place in the stream stream.

Listing 2.2: Measuring time with CUDA events.

```

// Declare variables

2 float millis;

cudaEvent_t start, stop;

cudaStream_t stream;

4

5

// Create events

cudaEventCreate(start);

7

cudaEventCreate(stop);

8

9

10

// Insert events into stream

cudaEventRecord(start, stream);

11

cudaSomeAsyncOperation(..., stream);

12

cudaEventRecord(stop, stream);

13

14

15 // Wait for events to finish before computing time

cudaEventSynchronize(stop);

cudaEventElapsedTime(&millis, start, stop);

```

Lines 7 and 8 create the events that will wrap the operation to be timed. Lines 11 and 13 insert the start and stop events around the operation to be timed. Line 16 blocks until the events have finished, then line 17 produces the milliseconds elapsed between the start and stop events.

### 2.7.2 CUDA Profiling Tools Interface

The CUDA Profiling Tools Interface [44] (CUPTI) "provides...detailed information about how applications are using the GPU in a system." Users may inject code into the entry and exit point of every CUDA C runtime and CUDA driver API function call. Additionally, users may configure and query hardware and software event counters to get insight into the operation of the GPU and CUDA stack. The event counters include instruction count, instruction throughput, memory loads/stores, memory throughput, cache hits/misses, branches and custom profile triggers. Chapter 6 describes how CUPTI can be used to record memory allocations, kernel arguments, and timestamps to build a model of the application execution.

#### 2.7.3 LD\_PRELOAD

LD\_PRELOAD [45] is a mechanism by which the ld linker will load additional user-specific shared objects before any others. If a function definition is present in a pre-loaded shared object, it will override the implementation present in later objects. When combined with dlsym() [46], it can be used to inject code into the entry of library calls in dynamically-linked binaries. Chapter 6 describes how LD\_PRELOAD can be used to infer information about application activity based on generic library calls.

## 2.8 Benchmark Library

This work makes use of the Google Benchmark library [47] as a harness for the developed custom microbenchmarks. Benchmark automatically determines the number of iterations to run based on the number of inputs and the desired CPU time. Benchmark allows repeated runs, and can report individual and aggregated statistics. This work makes uses of repeated runs, and presents results in terms of mean values and standard deviations. Benchmark also supports manual or automatic timing. An example of the basic layout of an automatic timing benchmark is shown in Listing 2.3. Microbenchmarks using Benchmark are written in C++, and have a setup phase, an interaction phase, and a teardown phase.

Listing 2.3: Benchmark with automatic timing.

```

1 #include <benchmark/benchmark.h>

static void BM_Foo(benchmark::State& state) {

3

for (auto _ : state) {

4

state.PauseTiming();

5

// Time elapsed here will not be counted

6

state.ResumeTiming();

7

foo();

8

}

9

}

10

BENCHMARK (BM_Foo);

```

Lines 2-9 define a Benchmark function, which is registered to be run in line 10. The loop body in lines 4 through 7 is executed and timed automatically by the framework, and the average time is recorded. Any part of the loop body that should not be timed can be wrapped in state.PauseTiming() and state.ResumeTiming(). This allows for per-iteration setup code to not be timed. The number of loop iterations is automatically controlled by the benchmark suite based on the number of arguments and desired run time. For the benchmarks presented in this work, there are tens of thousands of iterations for small transfers, and as few as a single transfer test for large iterations. The mean time is reported as a result of the benchmark. This process is then repeated multiple times to determine a standard deviation of the measurement.

Some of the microbenchmarks in this work make use of CUDA events to accurately measure the time taken by various CUDA operations. Benchmark supports this by allowing each microbenchmark to record and report its own iteration time. For example, consider Listing 2.4.

Benchmark provides a DoNotOptimize(<expr>) function, which forces the result of <expr> to be placed in a register. It does not prevent any optimization of <expr>, including replacing it with a statically-known value. Benchmark also provides a ClobberMemory() function, which forces all pending global memory writes to be completed. Through these two functions, the microbenchmarks can ensure that specific memory operations are completed and not optimized away.

Listing 2.4: Benchmark with manual timing.

```

1 #include <benchmark/benchmark.h>

2

static void BM_Foo(benchmark::State& state) {

3

cudaEvent_t start, stop;

4

cudaEventCreate(start);

5

cudaEventCreate(stop);

6

float msec;

7

8

for (auto _ : state) {

9

cudaEventRecord(start, NULL);

10

... // cuda operation to benchmark

11

cudaEventRecord(stop, NULL);

12

cudaEventSynchronize(stop);

13

cudaEventElapsedTime(&msec, start, stop);

state.SetIterationTime(msec / 1000);

14

}

15

}

16

BENCHMARK(BM_Foo) -> UseManualTime();

```

Now, when the benchmark is registered in line 17, the framework is informed that the benchmark loop iteration will report its own time. Instead of the framework timing the loop body in lines 9-14, CUDA events are used to measure the operation time. The iteration time is manually set in line 14.

Although Benchmark also supports multithreaded benchmarking, the microbenchmarks developed for this work do not use it. Benchmark does not directly support thread synchronization within each benchmark iteration, which is needed to accurately measure the performance of using multiple threads to move memory.

## 2.9 System Descriptions

Three high-performance heterogeneous systems are used in this work: an IBM S822LC for High Performance Computing [48], an IBM AC922 [49], and an Nvidia DGX-1 [29]. All systems feature multiple GPUs and multiple socketed CPUs. Their key differences are in CPU architecture (64-bit little-endian PowerPC for S822LC and AC922, x86-64 for DGX-1), number of GPUs (4 for the IBM machines, 8 for Nvidia), and GPU connection topology (NVLink 1.0 for S822LC, NVLink 2.0 for AC922, and hybrid PCIe 3.0 / NVLink 1.0

for DGX-1).

#### 2.9.1 Nvidia DGX-1

Table 2.7: Nvidia DGX-1 architecture summary.

| Component            | Specification                  |

|----------------------|--------------------------------|

|                      | 2x Intel Xeon E5-2698 v4       |

| $\mathbf{CPU}$       | 40C / 80T                      |

|                      | $2.2~\mathrm{GHz}$             |

| System Memory        | 512 GB DDR4                    |

| GPU                  | 4 Nvidia P100                  |

| CPU/GPU Interconnect | NVLink 1.0 (1 lane) / PCIe 3.0 |

| CUDA                 | 8.0, driver 384.125            |

| Kernel               | 4.4.0-79                       |

Figure 2.5: Nvidia DGX-1 architecture schematic. Interconnect legends are subtitled with theoretical maximum transfer rates. Each of the four NVLink lanes on a GPU is used to connect it to one other GPU. CPUs are connected to GPUs by PCIe  $3.0\ x16$  interconnects.

Table 2.7 and Figure 2.5 summarize the Nvidia DGX-1 system architecture. The Nvidia DGX-1 machine consists of two symmetric sections [29]. Each section consists of one 20-core Intel Xeon E5-2698v4 CPUs with 2-way SMT. Each CPU is connected to 256GB of DDR4 RAM, and each section makes up a Linux NUMA node. Each section has 4 Nvidia Tesla P100 GPUs coupled by single NVLinks. The sections are connected by an Intel 9.6GT/s QPI bus

between the CPUs providing 38.4 GB/s of bidirectional bandwidth, as well as NVLinks between corresponding GPUs. The first CPU socket hosts the majority of the PCI devices on the system, including the network interfaces and the disks. The CPU/GPU device affinity is relatively simple: CPU0 is directly connected to GPUs 0-3 and CPU1 is directly connected to GPUs 4-7. Every GPU is directly connected to all local GPUs in its cluster, as well as one outside.

### 2.9.2 IBM S822LC for High Performance Computing

Table 2.8: IBM S822LC architecture summary.

|                      | Specification         |

|----------------------|-----------------------|

|                      | 2x IBM Power8         |

| $\mathbf{CPU}$       | 20C / 80T             |

|                      | $4~\mathrm{GHz}$      |

| System Memory        | 512 GB DDR4           |

| GPU                  | 4 Nvidia P100         |

| CPU/GPU Interconnect | NVLink 1.0 (2 lanes)  |

| CUDA                 | 9.1.85, driver 390.31 |

| Kernel               | 4.4.0-96              |

Table 2.8 and Figure 2.6 summarize the hardware configuration. The IBM S822LC machine features two POWER8 CPUs and four Nvidia P100 GPUs [48]. Each POWER8 CPU has 10 cores, with 8-way simultaneous multithreading, and is attached to 256GB of DDR4 memory for a total of 160 threads and 512 GB of memory. Each POWER8 CPU and associated memory make up a Linux NUMA node. Each POWER8 CPU is part of a fully-connected triad of one POWER8 CPU and two P100 GPUs. Each device in the triad is connected by a gang of two NVLink 1.0 lanes for a total bidirectional bandwidth of 80 GB/s. The two triads are connected at the POWER8 CPUs by an IBM SMP X bus with 38.4 GB/s of bidirectional bandwidth.

Figure 2.6: IBM S822LC architecture schematic. Interconnect legends are subtitled with theoretical maximum transfer rates. The four NVLink lanes on a GPU are bonded into two two-lane pairs to connect it to the neighboring CPU and GPU.

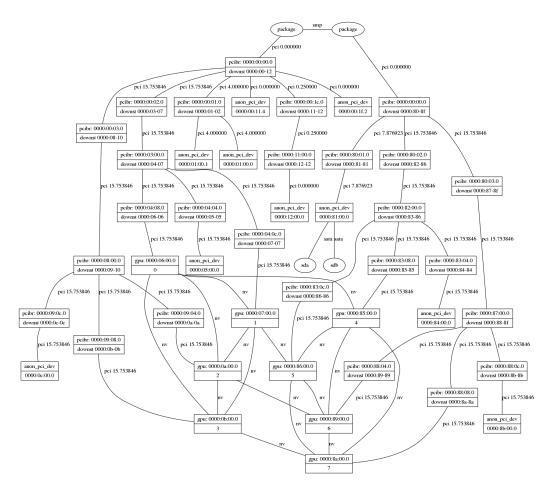

#### 2.9.3 IBM AC922

The IBM AC922 machine features two POWER9 CPUs and four Nvidia V100 GPUs [49]. Each POWER9 CPU has 20 cores, with 4-way simultaneous multithreading, and is attached to 512GB of DDR4 memory for a total of 160 threads and 1TB of memory. Each POWER9 CPU is part of a fully-connected triad of one POWER9 CPU and two V100 GPUs. Each device in the triad is connected by three bonded NVLink 2.0 lanes for bidirectional bandwidth of 150 GB/s. The two triads are connected at the POWER9 CPUs by an IBM SMP X bus with 64 GB/s bandwidth. Table 2.9 and Figure 2.7 summarize the hardware configuration. Like the S822LC, each triad is a Linux NUMA node.

Table 2.9: IBM AC922 architecture summary

|                      | Specification         |

|----------------------|-----------------------|

|                      | 2x IBM Power9         |

| $\mathbf{CPU}$       | $40C\ 160T$           |

|                      | $3.0~\mathrm{GHz}$    |

| System Memory        | 1TB DDR4              |

| GPU                  | 4 Nvidia V100         |

| CPU/GPU Interconnect | NVLink 2.0 (3 lanes)  |

| CUDA                 | 9.2.85, driver 396.15 |

| Kernel               | 4.14.0-49             |

Figure 2.7: IBM AC922 architecture schematic. Interconnect legends are subtitled with theoretical maximum transfer rates. The six NVLink lanes on a GPU are bonded into two three-lane pairs to connect it to the neighboring CPU and GPU.

### CHAPTER 3

## SYSTEM CHARACTERIZATION

This chapter describes and approach to produce an empirical performance model of hardware when an application invokes communication activities through the CUDA API functions. This performance model is needed for understanding the measured performance results to be presented in the rest of this thesis. In particular, this chapter motivates a joint performance model of software abstractions and underlying hardware. It then describes an approach for enumerating hardware components and connections.

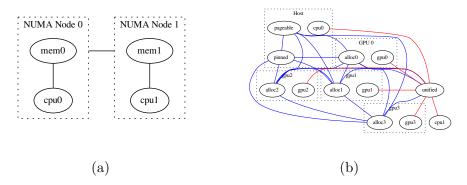

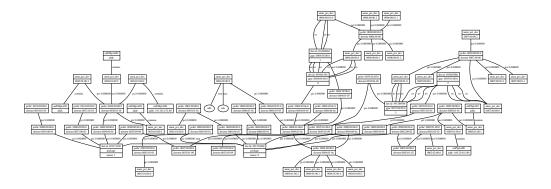

#### 3.1 Joint Abstraction and Hardware Model

Figure 3.1 shows two different communication abstractions of S822LC. Figure 3.1a represents the Linux NUMA view of the system. As described in Section 2.5, this view is accessible to the application through the libnuma library. Figure 3.1b represents the connectivity of the components through the CUDA API. Nodes in the graphs represent data storage locations or compute elements, and edges in the graph represent logical communication paths considered in this work. NUMA and CUDA present different abstractions, which are different from the system layout in Section 2.9.2. In practice, the logical communication paths available to the system are the union of these abstractions (and any other abstraction made available by the system).

Despite many of the logical communication paths using the same physical links, they achieve different performance on those links. As demonstrated in Chapters 4 and 5, some aspects of the empirical performance are determined by properties of the hardware links, while others are not. A communication performance model must therefore not only be based on the empirical performance of the logical links, but also incorporate understanding of the underlying hardware, if the model is to be applicable to more than just the

Figure 3.1: Communication topologies exposed to the application. (a) The abstraction presented by NUMA. (b) The abstraction presented by CUDA.

system it was developed on.

Ideally, while empirical communication performance is characterized, the mapping to underlying hardware should be automatically established. This work takes that mapping as a-priori, but the following section presents initial efforts to automate the process.

### 3.2 Topology Enumeration

This work proposes a two-step approach to establishing a mapping from logical communication paths to underlying hardware.

- 1. Generate a graph  $G_s$  of the hardware.

- 2. Observe hardware utilization while exercising logical communication paths.

The hardware is represented by a graph  $G_s = \{E, V\}$  where E is a set of edges representing communication links, and V is a set of vertices representing communication endpoints, or data routing elements. Sections 3.2.1 and 3.2.2 describe the specific system components explored. Each vertex in V is a data routing element. These vertices are able to receive and re-transmit data on any of their links. A PCIe switch is an example of a pure data-routing vertex. Optionally, the vertex may serve as a communication endpoint: a source or a sink for data. Processing elements and data storage elements serve as communication endpoints.

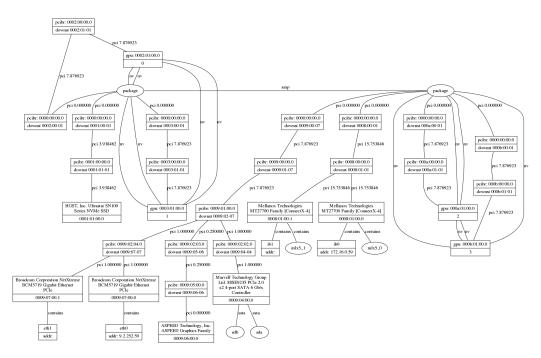

Hwcomm [50] is an open-source tool developed for automated hardware topology enumeration. This tool can be executed on a target system to generate  $G_s$  for that system. Thought hwcomm relies largely on exploring the PCIe device tree, it also uses information provided by the Nvidia Management Library [51] (NVML) to discover NVLink devices, and build a graph of hardware components. The first step of generating  $G_s$  is to discover the hardware components and connections through a multi-stage process.

#### Stage 1: Enumerate and Link CPU Sockets:

The Portable Hardware Locality [52] (hwloc) library is used to enumerate the present CPU sockets. As the test systems only have two sockets, all discovered sockets are considered to be directly connected by an SMP bus for the appropriate system type. The sockets and SMP buses are added to  $G_s$ .

#### Stage 2: Enumerate PCI devices:

The hwloc library is used to traverse the PCI device tree. All PCI devices are added to  $G_s$  and connected with PCI links of the appropriate type. Most attached storage, networking, and computing components are assigned an address in the PCI system and are discoverable in this step.

#### Stage 3: Update GPUs to Nvidia GPUs as appropriate:

Next, NVML is used to enumerate all Nvidia GPUs. The GPUs are matched by PCI address with existing PCI devices previously added to  $G_s$ , and NVML is used to discover whether NVLink is supported on each GPU and which other devices are connected to the GPU through NVLinks. This information is not provided by hwloc. The edges associated with the NVLinks are added to  $G_s$ .

### 3.2.1 Vertex Types

Table 3.1 summarizes the types of data routers discovered by hwcomm. These make up the vertices of  $G_s$ .

#### 3.2.2 Edge Types

In  $G_s$ , the vertices are connected by the discoverable edge types shown in Table 3.2.

Table 3.1: A summary of the types of data routers that can be discovered by hwcomm. Some components may also serve as data endpoints.

| Hardware                | Data Router | Data Endpoint |

|-------------------------|-------------|---------------|

| CPU Socket              | ✓           | $\checkmark$  |

| PCI Device              | ✓           | $\checkmark$  |

| PCIe Hostbridge         | ✓           | ×             |

| PCIe Bridge             | ✓           | X             |

| CUDA GPU                | ✓           | $\checkmark$  |

| Linux Block Device      | ✓           | <b>√</b>      |

| Linux Network Interface | ✓           | $\checkmark$  |

Table 3.2: A summary of the types of communication links that can be discovered by hwcomm. Some components may also serve as data endpoints.

| Edge Type | Description                                             |

|-----------|---------------------------------------------------------|

| SMP Bus   | A symmetric multiprocessing bus connecting two CPU      |

|           | sockets.                                                |

| PCIe Bus  | A PCIe link connecting a PCIe Bidge and PCIe device or  |

|           | PCIe Hostbridge and PCIe bridge.                        |

| NVLink1   | A first-generation NVLink connecting two Nvidia GPUs or |

|           | an Nvidia GPU and CPU                                   |

| NVLink2   | A second-generation NVLink connecting two Nvidia GPUs   |

|           | or an Nvidia GPU and CPU                                |

| SATA bus  | A Serial AT Attachment link conneting a host bus to a   |

|           | mass storage device.                                    |

#### 3.2.3 Discovered Topologies

The topologies of the S822LC, AC922, and DGX-1 systems are show in Appendix 8.

### 3.2.4 Logical Path to Hardware Link Mapping

Once the system graph is established, the mapping between logical communication paths and system graph vertices and edges can be established by observing performance counters while benchmarking logical paths. For example, NVML provides access to NVLink performance counters. As known quantities of data are moved across the logical connections, the hardware link performance counters can be observed to associate logical transfers with traffic across physical links.

In this work, automatic determination of the mapping is not considered; instead, the mapping for the case study systems is known ahead of time.

# CHAPTER 4

## EXPLICIT MEMORY PERFORMANCE

This chapter examines the performance of explicit data transfers over logical communication links presented in a system with NUMA and CUDA interfaces. In particular, it focuses on CPU/CPU transfers, CPU/GPU transfers, and GPU/GPU transfers. It highlights cases where the observed logical communication performance deviates significantly from the symmetries present in the CUDA API, numactl API, and hardware. Those deviations take the form of different performance on identical links, anisotropic link performance, or performance affected by device affinity.

The microbenchmarks developed for this section are available in the microbench project [53]. That project also includes benchmarks of other aspects of CUDA performance, including CUDA primitives like kernel launches, and CUDA libraries such as cuBLAS and cuDNN.

## 4.1 CPU / CPU Transfers

This section begins by examining CPU-CPU transfer performance through cudaMemcpy. This attempts to provide insight into the CUDA performance when sending data from one CPU socket to another. Such a transfer would occur when data is sent from a CPU A to a GPU attached to another CPU B. The data would traverse the SMP bus between CPU A and CPU B, and the bandwidth of that bus could limit the overall performance of the transfer. Algorithm 4.1 describes the measurement approach. During the setup phase, an allocation is created on the source CPU src and destination CPU dst. During the benchmark iterations, the dst cache is invalidated (if the src is different from the dst) by accessing that data from the src. Then, cudaMemcpy is invoked to transfer data between those allocations. CUDA events are used to measure the time of the memory copy.

Algorithm 4.1 Algorithm to measure cudaMemcpy CPU-CPU Bandwidth. AllocPinned and AllocPageable are defined in Algorithm 4.2. numa\_bind\_node is defined in Listing 2.1.

```

1: function BANDWIDTH(dst, src, transfer\_size)

2:

numa\_bind\_node(src)

srcPtr \leftarrow AllocPageable(transfer\_size)

3:

memset(srcPtr, 0, transfer\_size)

4:

numa\_bind\_node(dst)

5:

dstPtr \leftarrow AllocPinned(transfer\_size)

6:

memset(dstPtr, 0, transfer\_size)

7:

8:

start \leftarrow \text{cudaEventCreate}()

9:

stop \leftarrow \text{cudaEventCreate}()

for state do

▶ Benchmark library loop

10:

numa\_bind\_node(src)

11:

memset(srcPtr, 0, transfer\_size)

\triangleright invalidate dst cache

12:

numa\_bind\_node(dst)

13:

cudaEventRecord(start)

14:

cudaMemcpy(

15:

dstPtr, srcPtr, transfer\_size,

cudaMemcpyHostToHost)

16:

\operatorname{cudaEventRecord}(stop)

cudaEventSynchronize(stop)

17:

millis \leftarrow \text{cudaEventElapsedTime}(start, stop)

18:

state.SetIterationTime(\frac{millis}{1000})

19:

end for

20:

21: end function

```

Algorithm 4.2 shows different kinds of host allocation strategies used in microbenchmarks that need CUDA host allocations on particular NUMA nodes. AllocPageable simply defers to malloc, which will return memory allocation on a previously-pinned NUMA node. AllocPinned defers to malloc to get a NUMA allocations, and then uses cudaHostRegister to pin that memory. AllocWriteCombined uses the cudaHostAlloc CUDA library call with the cudaHostAllocWriteCombined flag to request that CUDA allocate write-combining memory.

**Algorithm 4.2** Pageable, pinned, and write-combining host allocators.

```

1: function AllocPageable(bytes)

ptr \leftarrow 0

2:

malloc(ptr, bytes)

3:

4:

return ptr

5: end function

6: function AllocPinned(bytes)

7:

ptr \leftarrow 0

malloc(ptr, bytes)

8:

cudaHostRegister(ptr, bytes, cudaHostRegisterPortable)

9:

10:

return ptr

11: end function

12: function AllocWriteCombined(bytes)

13:

ptr \leftarrow 0

cudaHostAlloc(ptr, bytes, cudaHostAllocWriteCombined)

14:

15:

return ptr

16: end function

```

Figure 4.1 shows intra- and inter-CPU cudaMemcpy performance on S822LC, AC922, and DGX-1. In all cases, for small transfers, the bandwidth is limited by the overhead of invoking the transfer. For intermediate and larger sizes, that overhead ceases to be the performance-limiter. At large sizes, intra-CPU bandwidth is higher, presumably since data transfer over the SMP bus is not required. The bandwidth saturates at the rate that a single thread can generate loads and stores.

S822LC and AC922 have similar intra-CPU performance except for intermediate sizes, where the S822LC performance peaks (presumably due to transfers happening in cache) and AC922 performance drops. On DGX-1, inter-CPU transfers are actually faster than intra-CPU transfers for intermediate sizes.

Figure 4.1: CPU-to-CPU transfer bandwidth vs. transfer size. Each transfer is measured using Algorithm 4.1. Whiskers at each point show the standard deviation measured over 5 repetitions.

# 4.2 CPU / GPU Transfers

Explicit CPU-GPU transfers are caused by the cudaMemcpy family of functions being invoked on one pointer to a host allocation and one pointer to a device allocation. In this work, the host allocation is created by one of three methods shown in Algorithm 4.2. The device allocation is created by cudaMalloc. This section compares bandwidth achievable from pinned, pageable, and write-combining host allocations, with particular emphasis on how device affinity affects transfer-performance and cases where transfers are anisotropic.

Algorithm 4.3 is used to evaluate the achievable bandwidth for cudaMemcpy transfers between a GPU allocation and a pageable, pinned, or write-combining host allocation. The same algorithm can be used for these cases, because the same cudaMemcpy CUDA API call to transfer data can be used on a pointer pointing to any of the allocation types. Depending on the source and destination types src and dst, and the desired host allocation type, the corresponding CUDA or numactl APIs are called to bind later activities to the desired GPU or CPU. Then, the CUDA or host allocators are invoked to produce devPtr (a pointer to the device allocation) and hostPtr (a pointer to the CPU allocation). The main benchmark loop uses the cudaMemcpy time as the iteration time that should be reported.

Algorithm 4.3 Measuring CPU/GPU bandwidth with cudaMemcpy. Host allocators are described in Algorithm 4.2. numa\_bind\_node is defined in Listing 2.1.

```

1: function BANDWIDTH(dst, src, bytes, num_iters)

if src is GPU then

2:

cudaSetDevice(src)

3:

4:

else

\triangleright src is CPU

numa\_bind\_node(src)

5:

end if

6:

7:

if dst is GPU then

cudaSetDevice(dst)

8:

\triangleright dst is CPU

9:

else

numa\_bind\_node(dst)

10:

end if

11:

devPtr \leftarrow \text{cudaMalloc}(bytes)

12:

hostPtr \leftarrow hostAllocate(bytes)

▷ appropriate host allocator

13:

if src is GPU then

14:

srcPtr \leftarrow devPtr

15:

dstPtr \leftarrow hostPtr

16:

else

\triangleright src is CPU

17:

18:

srcPtr \leftarrow hostPtr

dstPtr \leftarrow devPtr

19:

end if

20:

start \leftarrow \text{cudaEventCreate}()

21:

end \leftarrow \text{cudaEventCreate}()

22:

for state do

23:

cudaEventRecord(start)

24:

cudaMemcpy(dstPtr, srcPtr, bytes, cudaMemcpyDefault)

25:

\operatorname{cudaEventRecord}(stop)

26:

millis \leftarrow \text{cudaEventElapsedTime}(start, stop)

27:

state.SetIterationTime(millis / 1000)

28:

end for

29:

return elapsed

30: end function

```

#### 4.2.1 Comparison of Pageable, Pinned, and Write-Combining Host Allocations

To contextualize other results presented in this chapter, Figure 4.2 shows the transfer performance between pageable, pinned, and write-combined allocations on CPU0 and a device allocation on GPU0. On all tested systems, this is a local transfer between a directly-connected CPU and GPU. These performance curves exhibit features common throughout this chapter:

- For small transfer sizes, the time is dominated by overhead of invoking the transfer.

- For large transfer sizes, the performance is dominated by the exercised pysical link (in pinned or write-combining transfers) or some part of the abstraction layer (pageable transfers).

- The performance may vary smoothly across intermediate transfer sizes, or exhibit more complicated behavior. For example, in the AC922 transfer shown in Figure 4.2a, bandwidth peaks and then drops for intermediate transfer sizes before recovering for larger transfers.

Figure 4.2: CudaMemcpy bandwidth vs. transfer size for CPU0 to GPU0 transfers from (a) pageable allocations, (b) pinned allocations, and (c) write-combining allocations and GPU0 to CPU0 transfers of the same kind (d-f). Results for S822LC, AC922, and DGX-1 systems are shown. Whiskers show standard deviations of benchmark measurements over five repetitions.

The curves for transfers involving pinned or write-combined allocations on CPU0 (Figures 4.2(b,c,e,f)) share a similar shape: the transfer bandwidth is low for small sizes, and eventually saturates once transfers become large enough. S822LC and DGX-1 achieve  $\sim 75\%$  of the theoretical 40 and 20 GB/s bandwidths of the NVLink 1.0 x2 and PCIe 3.0 x16 links, respectively. AC922 achieves nearly 100% of the theoretical 75 GB/s unidirectional NVLink 2.0 x3 bandwidth.

In contrast, Figures 4.2a and 4.2d show transfers involving pageable allocations. The achievable bandwidth for large transfer sizes on S822LC is reduced to approximately 25% of the theoretical 40 GB/s bandwidth provided by the link. On AC922 the performance is nearly 50% of the theoretical bandwidth. AC922 CPU-to-GPU transfers also show a high bandwidth achieved for large CPU-to-GPU transfers, but not for GPU-to-CPU transfers. DGX-1 bandwidth peaks at 50% of the theoretical 20 GB/s of one-lane NVLink 1.0, but drops substantially for large transfer sizes.

Section 2.4.2 describes how cudaMemcpy from a pageable allocation to the GPU actually causes two data copies: one from the pageable allocation application to a pinned buffer, and a second copy, a DMA from the pinned buffer to the GPU. When pinned memory transfers are faster than pageable memory, we can infer that the CPU memory copy from pageable allocation to pinned buffer is limiting the performance. For comparison, consider Figure 4.1, which shows the performance of using cudaMemcpy to only do a copy from a pageable allocation to a pinned allocation. For S822LC, the pageable-to-GPU transfer shown in Figure 4.2a is approximately the same performance as the pageable-to-pinned transfer shown in Figure 4.1.

Surprisingly, on AC922, the pageable-to-GPU transfer for large transfer sizes is substantially faster than the pageable-to-pinned transfer that it should be limited by. This suggests that there is a different implementation for the two cases. Bandwidth spikes at intermediate sizes suggest that the GPU DMA may directly access data from the CPU cache when the transfer can fit in the cache. This is further reinforced by the lack of difference between pinned and write-combining transfer bandwidth, which suggests that caching or lack thereof on these systems does not influence the DMA engine.

#### 4.2.2 CPU/GPU Bandwidth Measurements

Figure 4.3 shows CPU/GPU bandwidth on a variety of logical paths for S822LC, AC922, and DGX-1. Transfers involving pinned and pageable allocations are shown. Write-combined results are omitted as they match the pinned performance.

Figure 4.3: Transfer bandwidth vs. transfer size for local and remote transfers from pageable and pinned host allocations on S822LC, AC922, and DGX-1. (a-c) Transfers from pageable allocations to GPUs. (d-f) Transfers from pinned allocations to GPUs. (a) and (d) are for S822LC, (b) and (e) for AC922, and (c) and (f) for DGX-1.

In general, the bandwidth follows the same outline described in Section 4.2.1, with overhead-dominated time for small transfers, bandwidth-dominated time for large transfers, and some other behavior between. There are some distinctive reoccurring patterns in Figures 4.3 (a)-(c).

CPU-to-GPU pageable transfers on the IBM systems exhibit peaks in transfer bandwidth at intermediate transfer sizes. The shape of this curve suggests some insight into the copy implementation. For example, consider the S822LC CPU0 to GPU0 curve. The expected process is that a pageable allocation on CPU0 is copied to one or more pinned allocations on CPU0, which are then accessed by GPU0's DMA engine. The fact that the peak bandwidth at intermediate transfer sizes surpasses the measured bandwidth